Power

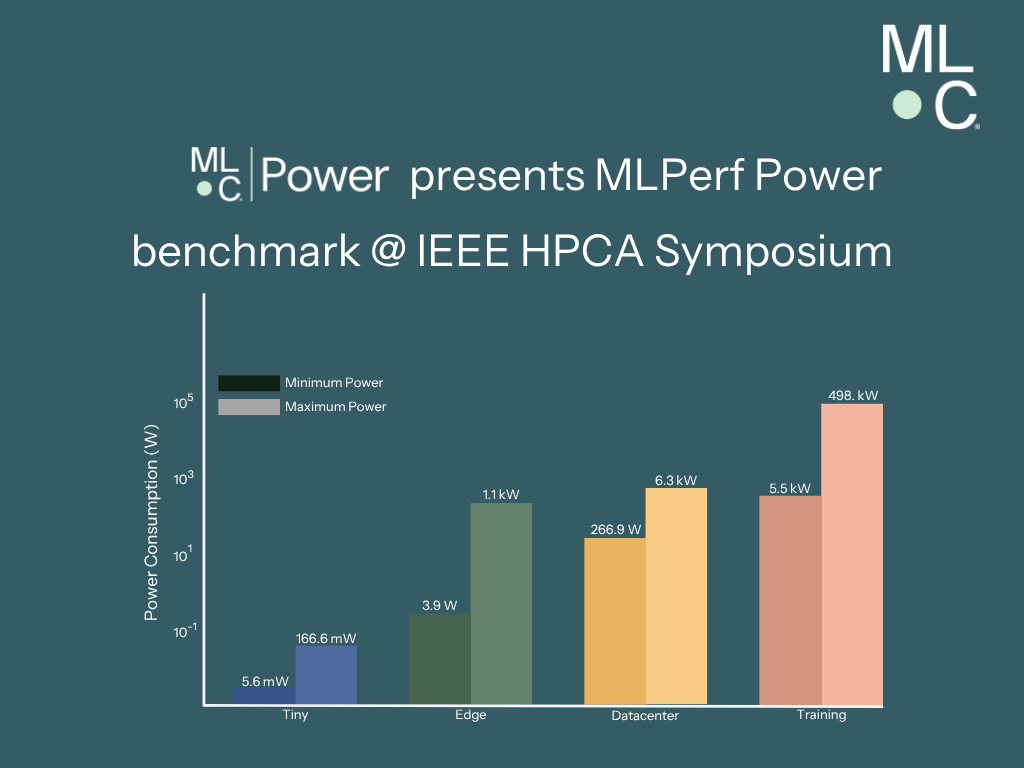

Create power measurement techniques for various MLPerf benchmarks that enable reporting and comparing energy consumption, performance and power of benchmarks run on submission systems.

Purpose

Power consumption and energy efficiency are critical challenges for deploying and operating machine learning systems across the spectrum, from battery-powered smartphones to the world’s largest data centers. The Power working group will create tools to measure power for machine learning systems to evaluate efficiency and guide system optimization and design trade-offs.

Deliverables

- Power measurement techniques built on industry-standard tools

- List of approved power analyzers

- Power result metrics and format

- Initial deliverable is integration with MLPerf Inference v1.0 for wall-powered systems

- Roadmap for battery-powered system and MLPerf Training

Meeting Schedule

Tuesday December 9, 2025 Weekly – 15:05 – 16:00 Pacific Time

How to Join and Access Power Resources

The Power working group is limited exclusively to MLCommons members and affiliates. If you are not already a member or affiliate or part of a member or affiliate company, you can learn more about MLCommons membership here.

To sign up for the group mailing list, receive the meeting invite, and access shared documents and meeting minutes:

- Fill out our subscription form and indicate that you’d like to join the Power Working Group.

- Associate a Google account with your organizational email address.

- Once your request to join the Power Working Group is approved, you’ll be able to access the Power folder in the Members Google Drive.

To engage in working group discussions, join the working group’s channels on the MLCommons Discord server.

To access the GitHub repository (public):

- If you want to contribute code, please submit your GitHub ID to our subscription form.

- Visit the GitHub repository.

Power Working Group Chairs

Chairs

To contact all Power working group chairs email [email protected].